1. 從Flash系統的性能提升說起

從SD卡、手機、平板等消費級產品到數據中心企業級場景,NAND Flash憑借其高性能、大容量、低功耗以及低成本等特性大受歡迎,是目前應用最為廣泛的半導體非易失存儲介質。為了滿足業務場景越來越嚴苛的性能要求,人們想了許多方法來提升基于NAND Flash的系統性能,具體可分為以下幾類:

圖一 Flash系統性能提升概覽

- 提升總線頻率,優化AC Timing:在滿足可靠傳輸的基礎上,提升NAND Flash總線頻率,盡可能使用較小的時序參數進行操作。特別是在Page Size越來越大(2K 4K 8K 16KB)的情況下,優化時序參數從而減小數據在總線上的傳輸時間顯得尤為重要,這也是過去二十多年來人們一直在持續努力的方向,比如總線接口速率為200Mbps (100MHz)時,完成4KB數據傳輸需要大約40us,但如果將總線接口速率提升到1600Mbps (800MHz)時,完成4KB數據傳輸僅需要大約5us。

- 使用Cache Read/Program: 一般情況下,LUN(Logic Unit Number)是NAND Flash最小的邏輯操作單元,讀/寫操作是串行執行的,即一個讀/寫命令完成后,才能進行下一個讀/寫操作。Cache Read/Program允許用戶在NAND Flash Array Busy時,同時在總線上進行讀/寫數據傳輸,從而提高流水效率。

- 多路并發技術包括:1)通道間并發,允許用戶在不同的通道上并發執行獨立的命令和數據操作;2)通道內并發,即Interleaving操作,允許用戶在滿足一定約束的情況下,在通道內的不同CE或CE內的不同Die之間進行交織操作;3)多平面操作,即Multi-Plane操作,允許用戶并發讀/寫Die內的不同Plane。可以說,正是因為有了多路并發技術,才使得基于NAND Flash的固態存儲產品能達到GB級別的讀/寫性能。

可見,以上優化覆蓋了NAND Flash基礎時序/指令優化到系統級的綜合優化,在實際應用中可以根據系統要求組合選用。經過多年發展,Cache Read/Program及多路并發技術已發展得較為成熟,近年來的變化相對較小,但NAND Flash總線頻率提升技術一直在蓬勃發展,并且近年來有加速演進的趨勢,下面我們將結合ONFI協議演進來感受一下NAND Flash接口速率的演進。

2. ONFI接口演進歷史

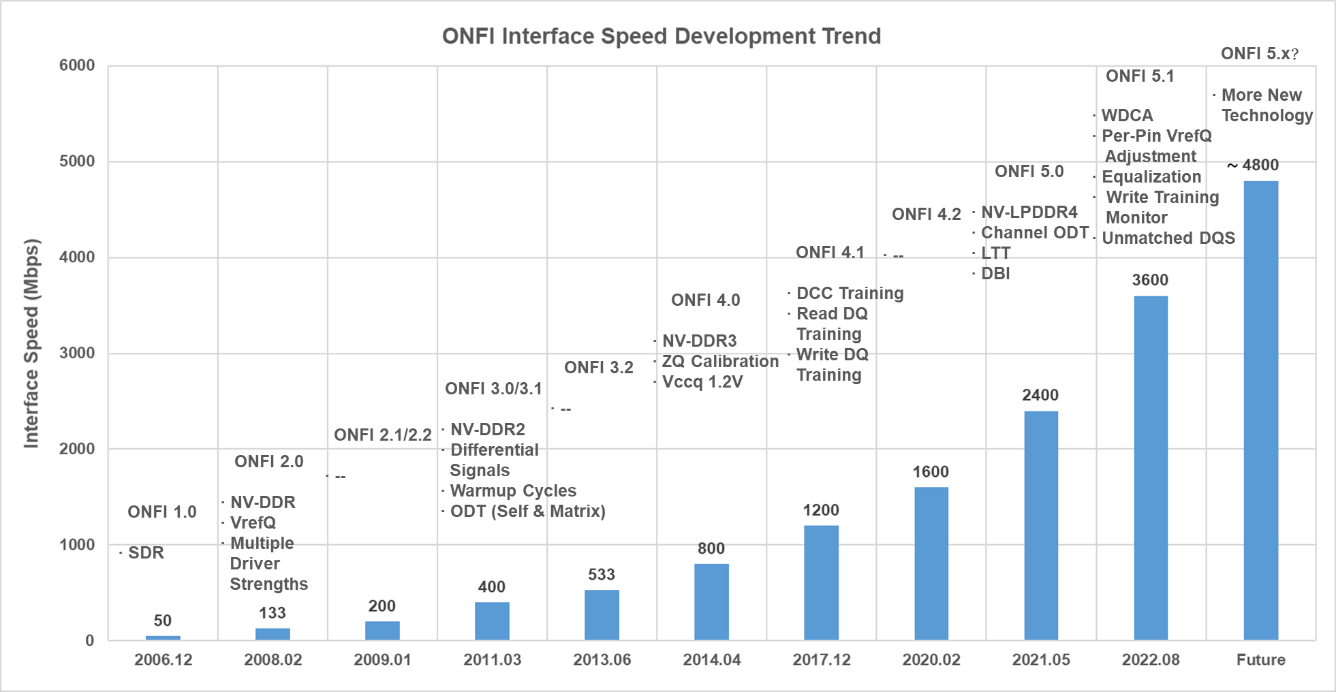

ONFI (Open NAND Flash Interface)組織成立于2006年5月,致力于簡化NAND Flash在消費電子應用和計算平臺中的集成和普及。自2006年12月發布第一個ONFI協議以來,ONFI組織已經累計發布了數十個版本,最大接口速率也從最初的50Mbps發展到目前最新的3600Mbps,從圖二可以看到ONFI協議不斷優化的接口演進趨勢。

圖二 ONFI接口速率演進

- ONFI 1.0:隨著NAND Flash在SD卡及IPod等消費級電子產品的成功應用,以及基于閃存的MP3、U盤等需求量不斷增大,極大地拓展了NAND Flash的應用領域。但由于不同NAND Flash廠家的接口協議各有不同,導致下游的主控廠商和產品制造廠商遇到各種兼容性問題。為了改變這種局面,Intel牽頭成立了ONFI組織,并在不久后迅速推出ONFI 1.0版本,目的是統一NAND Flash接口協議。

- ONFI 2.x:ONFI 2.x引入了NV-DDR技術,通過雙邊沿采樣(Double Data Rate)實現速率倍增,最大接口速率從ONFI 2.0的133Mbps演進到ONFI 2.1/2.2的200Mbps。NV-DDR技術引入外部參考電壓作為數據輸入/輸出信號的采樣基準,采用源同步時鐘來精確鎖存數據、命令、地址信號,但由于DQS和Clock不是差分信號,所以邊沿容易受干擾,目前主流消費級/企業級NAND Flash已經很少看到NV-DDR接口。

- ONFI 3.x:ONFI 3.x引入了NV-DDR2技術,最大接口速率從ONFI 3.0/3.1的400Mbps演進到ONFI 3.2的533Mbps。NV-DDR2引入了差分信號和On-Die Termination (ODT)技術來提升信號質量。在差分模式下,通過在數據傳輸階段使能RE_n/RE_c差分信號對和DQS_t/DQS_c signals差分信號對,可有效抑制噪聲和干擾。通過在NAND Flash芯片上集成ODT端接電阻,可以將控制器和NAND Flash的信號傳輸通道上的阻抗失配減少到最小,有助于減少信號反射;另外,ODT阻值可以通過軟件配置寄存器來控制,因此可以大大簡化硬件電路設計。

- ONFI 4.x:ONFI 4.x引入了NV-DDR3技術,最大接口速率從ONFI 4.0的800Mbps演進到ONFI 4.2的1600Mbps。為保障高速信號傳輸質量,NV-DDR3引入了多項校準技術,包括ZQ Calibration、Duty Cycle Correction (DCC)和讀/寫DQ校準。上文提到ONFI 3.0引入了ODT技術,由于NAND Flash上的ODT電阻采用CMOS工藝制備,容易在溫度和電壓變化時發生阻值漂移,因此需要通過ZQ Calibration技術通過外接高精度電阻進行阻值校準。DCC校準可調節信號占空比,解決高速信號傳輸路徑不對稱導致的上升沿與下降沿失配問題,而讀/寫DQ校準可以保證讀/寫采樣信號對準眼圖中心。

- ONFI 5.x:ONFI 5.x引入了NV-LPDDR4技術,最大接口速率從ONFI 5.0的2400Mbps演進到ONFI 5.1的3600Mbps。為了解決高速接口帶來的巨大信號完整性挑戰,ONFI 5.x除了進一步加強寫校準和VrefQ校準外,還引入了非對稱DQS設計和自適應均衡器設計。如DFE(ecision Feedback Equalizer,判決反饋均衡器)技術用上次信道的輸出經過判斷后加權反饋到輸入上,可以消除碼后干擾。另外,NV-DDR3和NV-LPDDR4支持的最大接口速率相同,但NV-LPDDR4的優勢在于采用LTT技術后可大幅度降低讀操作功耗。

從ONFI 1.0到近期最新發布的ONFI 5.1可以看出,為了匹配系統前端接口(如eMMC/UFS/PCIe)越來越高的帶寬要求,NAND Flash接口速率整整提升了72倍,而且未來還將快速走向下一個峰值。

那接口速率的提升給系統帶來的收益是否也在翻倍上漲呢?答案是否定的。

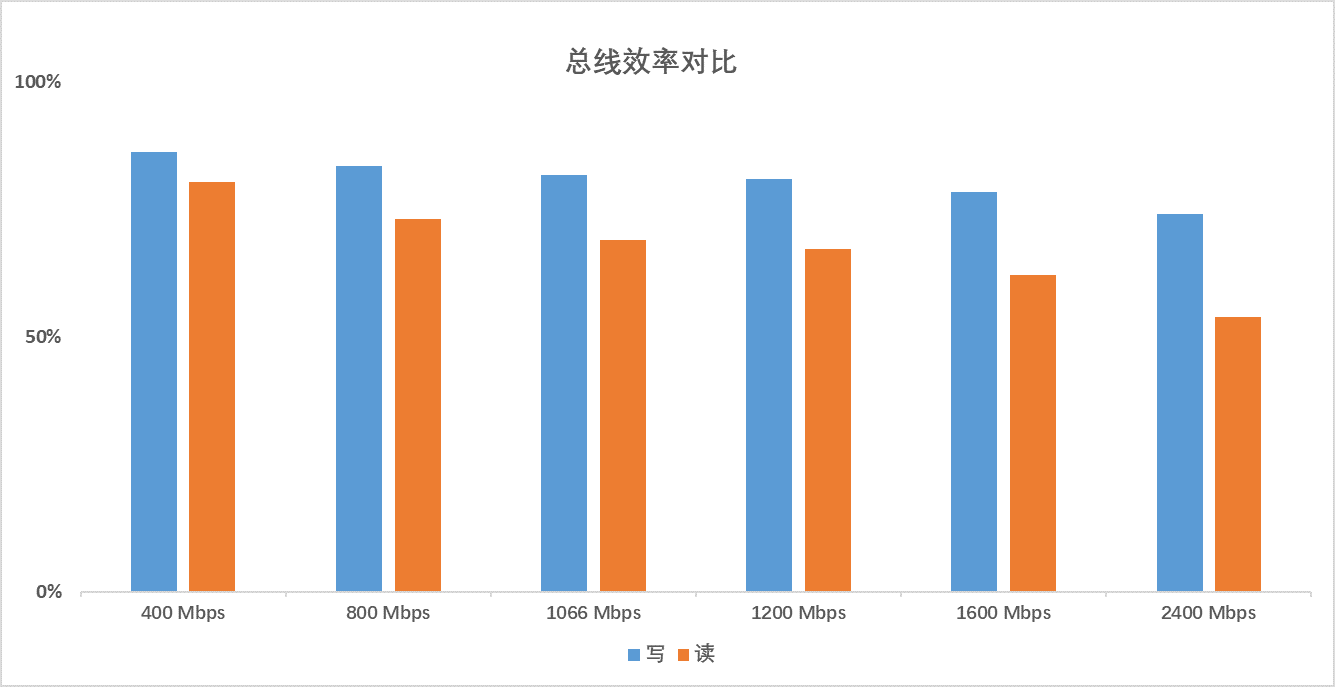

3. 傳統協議的不足呼喚進一步改進

NAND Flash總線上傳輸的信號可分為命令、地址和數據3種,通過DQ[7:0]時分復用,在不同的時刻分別傳輸命令、地址和數據。其中,數據是同步傳輸、差分采樣,速率較高;但命令和地址是異步傳輸、單端采樣,速率較低。從ONFI 1.0到ONFI 5.1,接口速率得到了飛速發展,但命令、地址和數據的傳輸形式基本不變。實際上,隨著總線速率提升,改善的主要是數據傳輸時延,命令和地址的傳輸時延并沒有得到改善,對系統而言總線使用效率是在不斷下降的。如下圖三在樂觀的場景下比較了寫/讀場景的總線效率,可以看到,讀和寫的總線效率都在逐漸降低,尤其是在讀場景跌落到50%左右時進一步加劇了系統設計的挑戰。

圖三 NAND Flash總線效率分析

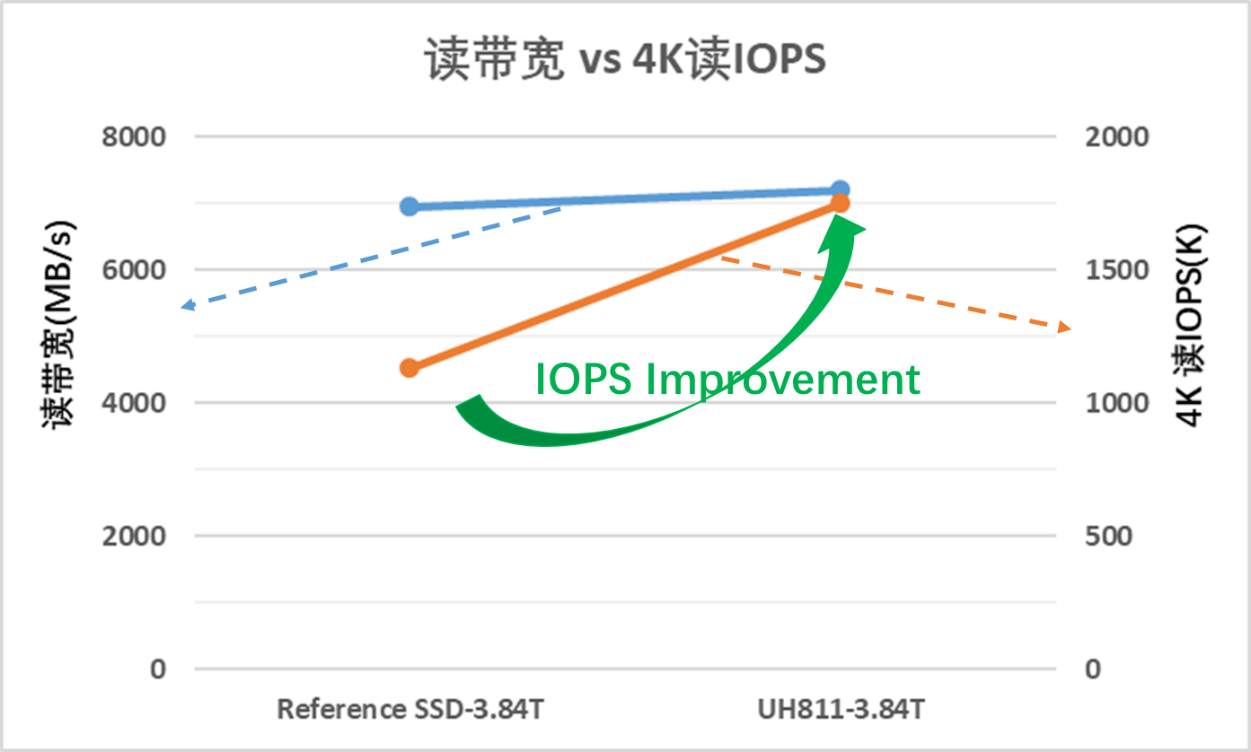

圖四以業內某型號SSD為參考,與憶聯企業級固態硬盤產品UH811a進行了對比分析。可以看到,兩款SSD的讀帶寬相當,都在7000MB/s左右,但UH811a的4K隨機讀IOPS相比參考SSD有顯著提升。進一步分析可以發現,將UH811a的4K IOPS換算成帶寬,是與讀帶寬相當的;但對參考SSD進行同樣的換算,則換算出來的帶寬只有讀帶寬的70%,原因就在于隨機讀操作的總線開銷高于順序讀。

圖四 讀帶寬 vs 4K讀IOPS

可見,在傳統命令/地址/數據傳輸形式不變的情況下,隨著接口速率提升,增加系統復雜度的同時,帶來的收益卻在衰減,因此,傳統協議的不足推動協議不斷改進。面對這個問題,JEDEC組織正緊鑼密鼓地討論協議的下一輪演進,未來將在提升接口速率的同時優化命令/地址傳輸方式,這也勢必會給主控設計帶來新的考驗。

4. 總結

一直以來,提升NAND Flash接口速率是提高系統性能的主要手段,NAND Flash廠商也想出了各種辦法來解決高速信號帶來的信號完整性問題。面向未來,傳統的命令/地址輸入方式導致總線利用率不高,協議的進一步演進除了考慮繼續提升接口速率外,也將迎來新的命令/地址輸入方式。憶聯將密切關注協議發展動態,并以靈活的架構來兼容支持未來的介質,給客戶帶來更好的存儲產品與解決方案。

參考資料:

1. ONFI spec:

http://www.onfi.org/specifications

2.2022, Phison, NAND Flash 101: Flash Device Interfaces:

https://phisonblog.com/nand-flash-101-flash-device-interfaces-2/

3.2021, 移動NAND閃存存儲的演進:

https://phisonblog.com/the-evolution-of-mobile-nand-flash-memory-storage-2/

4.芯片中的數學——均衡器EQ和它在高速外部總線中的應用:

https://zhuanlan.zhihu.com/p/48343011

地址:深圳市南山區記憶科技后海中心B座19樓

電話:0755-2681 3300

郵箱:support@unionmem.com